Phase Locked Loop(PLL), 위상 고정 루프

: 잘 정의된 위상 관계에서 두 주기 신호의 위상을 유지하는 폐쇄 루프 네거티브 *피드백 제어 시스템

*피드백 루프 - 궤환 회로, 입출력 사이의 위상차를 줄여준다.

해당 파일 기반으로 작성된 글입니다.

Part 1. PLL의 역할

● 안정적인 주파수를 생성하고, 흔들리지 않도록 고정해준다.

● 주파수를 정확하게 가변 할 수 있다.

● 신호 지연과 위상 변화가 존재하더라도 정확한 신호 해석이 가능하다.

※ 사용 이유

신호 지연과 전송 중의 위상 변화로 인해 디지털 신호를 정확하게 수신하고 해석하는 것은 쉽지 않다. 따라서 클럭의 시작과 끝을 정확히 맞춰주는 동기(Synchronization)가 필요하다.

→ 입력 신호가 어떻게 들어오든 간에 특정 위상점에서 들어오는 것처럼 고정한다.(Lock 한다)

Part 2. PLL의 기본 구조(Basic Structure)

Phase Detector(PD) : input(v)와 VCO에서 생성된 신호의 위상차에 비례하는 출력을 내보낸다.

→ 비교기, 두 개의 주파수 신호를 입력 받아 두개의 주파수, 위상차를 알아내는 역할. 그 차이에 해당하는 특정한 클럭을 생성하고 출력으로 내보냄.

Loop Filter(LF) : PD 출력의 고주파 AC 성분을 감쇠한다.

→ LPF형태의 구조이며 loop 동작 중 발생하는 잡음 신호를 걸러낸다.

커패시터를 이용하여 축적된 전하량 변화를 통해 VCO조절 단자의 전압을 가변 한다.

Voltage Controlled Oscillator(VCO) : ω_c에 대해 주파수가 이동되는 AC 신호 생성.

→ 입력 제어 전압(LF의 출력 전압)에 비례하는 주파수를 출력하는 발진기.

*ω_c : VCO의 중심 주파수(Centre Frequency) (감지할 주파수 범위에 따라 Feed-Forward Parameter로 PLL에 공급)

Part 3. PLL의 기본 방정식(Basic Equations)

● Input Signal

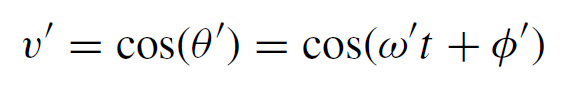

● VCO에 의해 생성된 신호

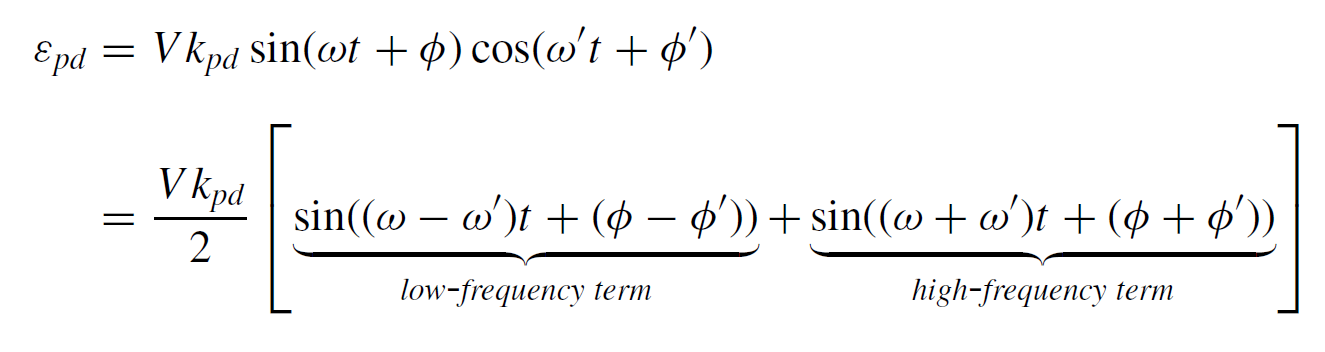

● 곱셈기 PD Output의 Phase Error Signal(위상각 에러 신호)

※ 삼각함수의 곱셈정리

sin(x)*cos(y) = 1/2 [sin(x+y)+sin(x-y)]

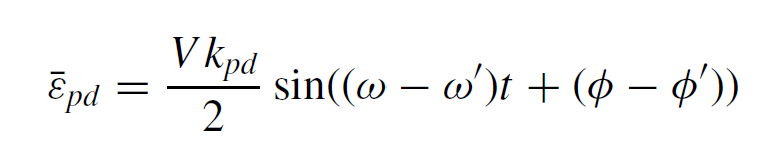

● LF에 의해 PD Signal의 고주파 성분 제거

● VCO가 입력 주파수에 잘 맞추어져 있다고 가정. ( ω ≒ ω')

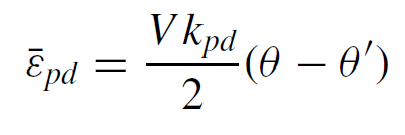

● 위상 오차 매우 작음( Φ ≒ Φ') → PD Output, 동작점 근처에서 선형화 가능하다.

● VCO의 평균 주파수

*잠김 상태(Locked State) - PLL이 Output signal과 Input signal을 동기화(Synchronization)(<=> PLL 정상동작)

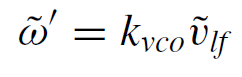

● VCO 주파수의 소신호 변화

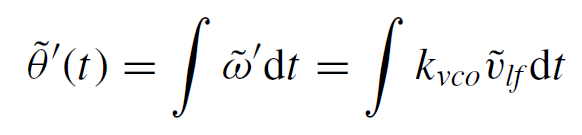

● PLL에 의해 감지된 위상각 변화

Part 4. Linearized Small Signal Model of PLL(선형화된 소신호 모델)

4-1. Equations of Linearized Small Signal Model (선형화된 소신호 모델 방정식)

● Phase Detector

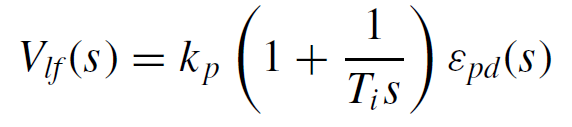

● Loop Filter

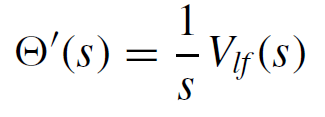

● Controlled Oscillator

4-2. Transfer Function (전달함수)

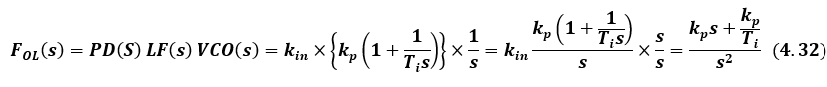

● Open-loop phase Transfer func

PLL이 원점에 2개의 극이 있는 유형 2 시스템.

정상상태 오류 없이 입력 위상각의 일정한 기울기 램프까지 추적한다.

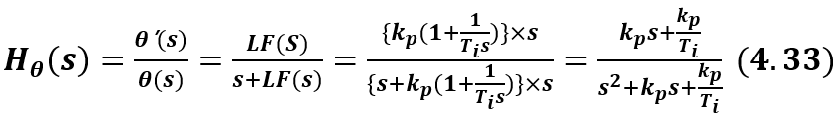

● Closed-loop phase Transfer func

PLL이 입력 위상각 검출 시 저역 통과 필터링 특성을 나타낸다.

입력 신호에서 발생 가능한 잡음 및 고조파로 인해 발생하는 감지 오류를 감쇠시킨다.

● Closed-loop error Transfer func

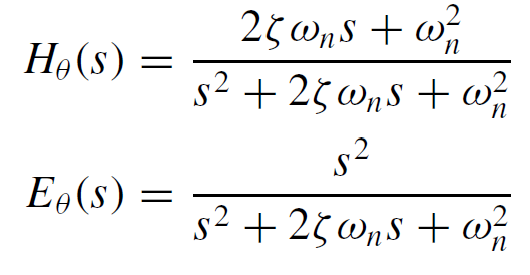

● 정착시간 (Settling time)

: 특정 2차 시스템의 step input에 대한 시작 시간부터 시스템이

정상상태 응답의 1% 이내로 유지되는 시간까지 측정한 시간

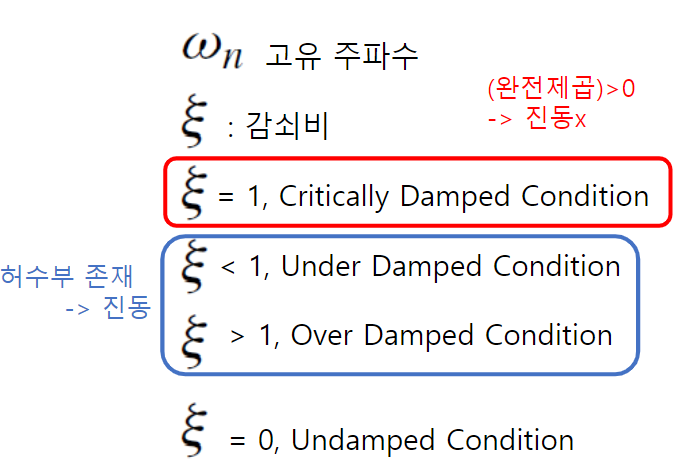

* ξ : 크사이

● 2차 전달함수의 정규화

● 튜닝 매개변수(tuning parameters)

단일 입력 신호(1V)라고 가정하였을 때,

Part 5. PLL Response (예시)

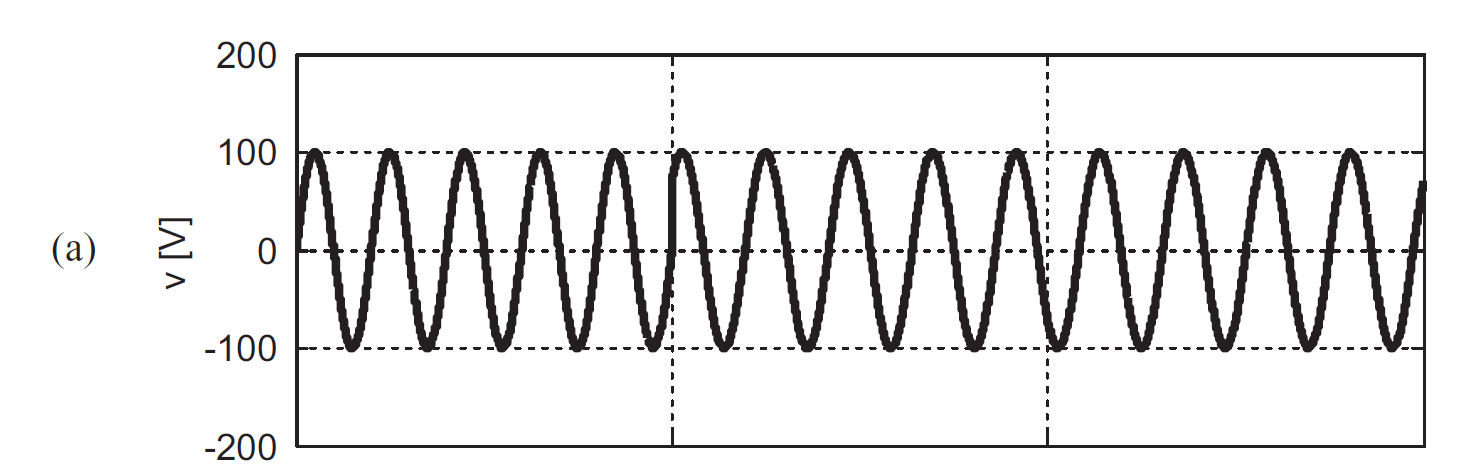

● Grid Voltage

● Real Grid Freq & Estimated Freq(PLL)

● Estimated Phase-angle

● Error(Phase-angle, Estimation)

고주파 항의 결과로 입력 전압의 주파수 및 위상각을 추정할 때 진동 정상 상태 오류가 발생한다.

Oscillatory Error Amplitude 해결

더 긴 정착시간 설정 ⇔ system Bandwidth 줄임

정착 오류의 크기 줄이는 방법은 (4.37)의 상수 횟수 늘린다. (첨부 파일의 식 보시면 됩니다.)

'학부 자료 > PLL' 카테고리의 다른 글

| [PLL] Phase Locked Loop, 위상 고정 루프, 선형·비선형 모델 비교, 위상각 점프와 주파수 변화 (143) | 2023.11.15 |

|---|